# Maximizing process efficiency with dual current exposure strategy

BEAMeeting E-Beam & Laser Workshop EIPBN 2024 La Jolla, CA May 28, 2024

Bernadeta Srijanto sijantobr@ornl.gov Center for Nanophase Materials Sciences (CNMS), ORNL A U.S. DOE Office of Science User Facility

ORNL is managed by UT-Battelle, LLC for the US Department of Energy

#### Center for Nanophase Materials Sciences (CNMS) is One of Five Nanoscale Science Research Centers (NSRCs) U.S. DOE Office of Science User Facilities

- We are a user facility, established by DOE

Office of Sciences

- We provide the resources that users need for their work in nanoscience : instruments and staff expertise!

We provide FREE ACCESS if the intent is to publish. Submit a proposa (2 calls/year) <u>https://www.ornl.gov/facility/cnms</u>

Molecular Foundry Lawrence Berkeley National Laboratory

Center for Nanoscale Materials Argonne National Laboratory

Center for Functional Nanomaterials Brookhaven National Laboratory

Center for Integrated Nanotechnologies Sandia National Laboratories Los Alamos National Laboratory

Center for Nanophase Materials Sciences Oak Ridge National Laboratory

Co-located with other BES user facilities (SNS and OLCF)

Fabrication of continuous, multiscale pattern (whether etched or metalized) can be lengthy, tedious

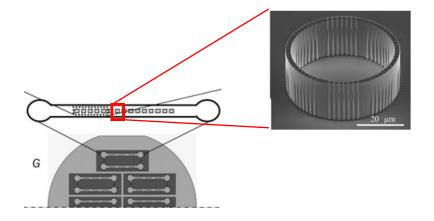

Example 1: nanowires and PADS

Fabrication process: EBL pattern nanowire (20-60nm width) Metal deposition + lift off Photolithography to pattern bigger pads (~100µm) Metal deposition + lift off Example 2: microbioreactor within microfluidic channel

Fabrication process: EBL pattern bioreactor, with 200nm slits Metal deposition + lift off Photolithography to pattern microfluidic channel Etch both bioreactor and microfluidic channel together

### We have an electron beam lithography system that allows dual current exposure

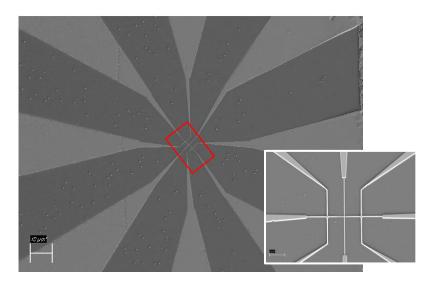

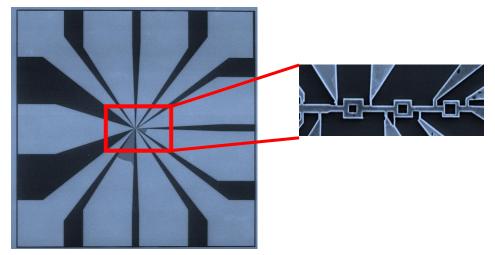

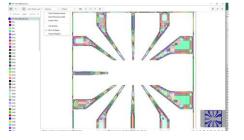

Simple device example fabricated using dual current exposure :

Larger features up to  $500 \mu m,$  smaller feature 200-300nm

## We have an electron beam lithography system that allows dual current exposure

Simple device example fabricated using dual current exposure :

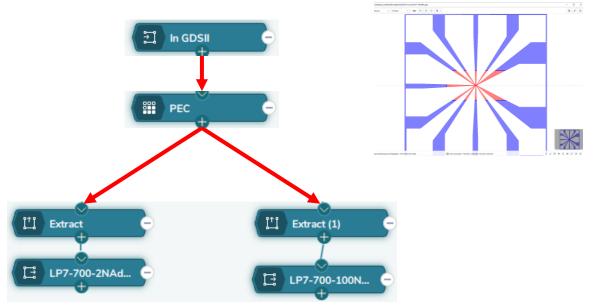

- 1. Layout preparation

- Select the cutoff feature size to be exposed at lower current vs at higher current

- Separate them into two layers.

- Draw some overlap layout where the two layers meet

- 2. Import gds

3. Run PEC before exporting the layout into two v30's

4. Extract, Heal, and Export

exposure (e.g. 1nA, 2nA)

v30 for higher current exposure (e.g. 40nA, 100nA)

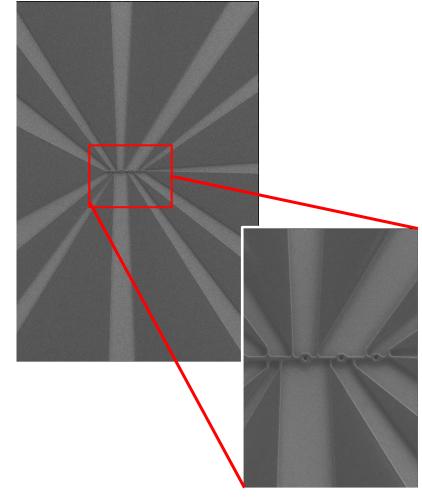

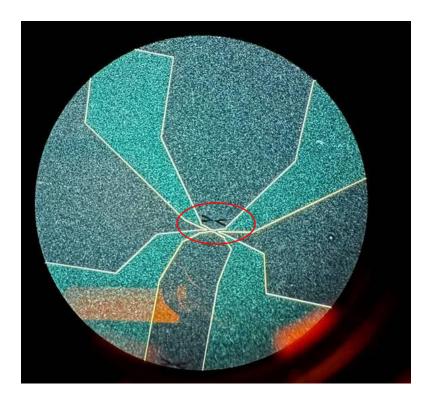

### SEM imaging of the exposure result:

Placing PEC before instead of after splitting the layers reduces/minimizes proximity effect of higher current exposure on smaller features.

6

There is still some challenge with offset in dual current exposure: patterns of two currents did not align properly, i.e., there is offset.

The offset is due to the (bounding box) of two layers do not share the same center location.

We fixed it by adding a very small feature (e.g., square) on four corners at the same position for both layers.

We are very interested if Beamer has a solution for this offset.

#### Dual current exposure save extra process steps and exposure time

Exposure time :

- 1. For 3x3 array of the device example on a 5-10 mm chip size:

- Exposure only at 2nA current took 5-6 hours.

- Dual current exposure (2nA and 100nA) took 1-2 hours

- 2. Exposure time saving is more significant when exposure is performed on 4" wafer.

- We had a pattern ranging from 20nm dots to several  $\mu$ m feature size, arrayed on 4" wafer.

- Exposure only at 2nA current : ~158 hours

- Dual current exposure (2nA and 40nA) : ~8 hours

- Dual current exposure (2nA and 100nA) : ~4.5 hours

Process step:

Only requires one lithography step, one deposition step

- the dual current exposure does not require alignment mark !

Thank you!

Questions? Comments?

9